时间:2024/5/23 阅读:757 关键词:MOSFET

对于分立式设计,功率FET的布置和封装尺寸对热回路ESR和ESL也有重大影响。

ADI对使用功率FET M1和M2以及解耦电容CIN的典型半桥热回路进行了建模和研究。

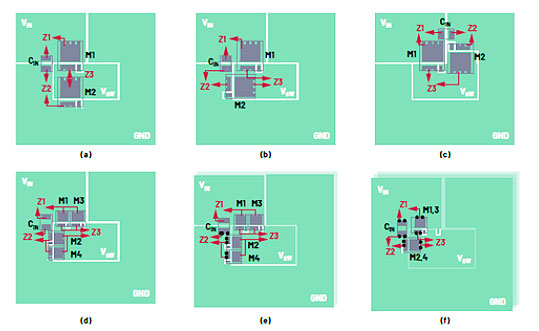

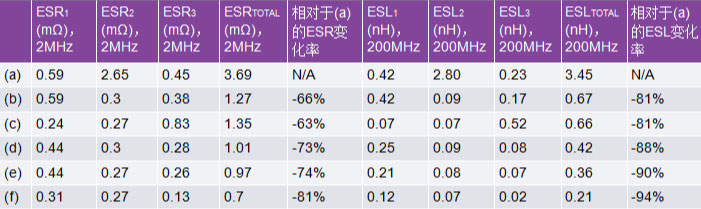

如下图所示,比较常见功率FET封装尺寸和放置位置,如下表每种情况下提取的ESR和ESL。

热回路PCB模型:

(a) 5mm * 6mm MOSFET,直线布置

(b) 5mm* 6mm MOSFET,以90°形状布置;

(c) 5mm* 6mm MOSFET,以180°形状布置;

(d) 两个并联的3.3mm * 3.3mm MOSFET,以90°形状布置;

(e) 两个并联的3.3mm * 3.3mm MOSFET,以90°形状布置,带有接地层;

(f) 对称的3.3mm * 3.3mm MOSFET,位于顶层和底层,以90°形状布置。

下表对于不同器件形状和位置,使用FastHenry提取的热回路PCB ESR和ESL

(a)至(c)展示:三种常见功率FET布置,其中采用5mm × 6mm MOSFET。热回路的物理长度决定了寄生阻抗。

与(a)相比,情况(b)中的90°形状布置和情况(c)中的180°形状布置的回路路径更短,导致ESR降低60%,ESL降低80%。由于90°形状布置显示出了优势,可基于情况(b)研究更多情况,以进一步降低回路ESR和ESL。

(d):将一个5mm × 6mm MOSFET替换为两个并联的3.3mm × 3.3mm MOSFET。由于MOSFET尺寸更小,回路长度进一步缩短,导致回路阻抗降低7%。

(e):将一个接地层放置在热回路层下方,与情况(d)相比,热回路ESR和ESL进一步降低2%。原因是接地层上产生了涡流,其感应出相反的磁场,相当于降低了回路阻抗。

(f):构建了另一个热回路层作为底层。如果将两个并联MOSFET对称布置在顶层和底层,并通过过孔连接,则由于并联阻抗,热回路PCB ESR和ESL的降低更加明显。因此,在顶层和底层上以对称90°形状或180°形状布置较小尺寸的器件,可以获得最低的PCB ESR和ESL。

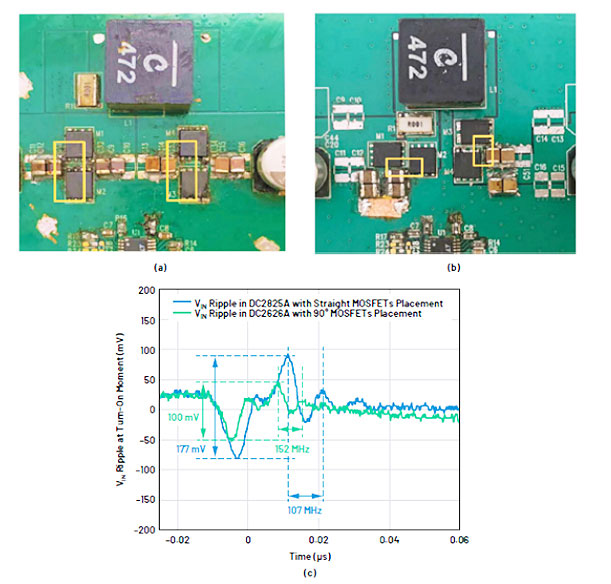

为了通过实验验证MOSFET布置的影响,可以使用ADI的高效率4开关同步降压-升压控制器演示板LT8390/DC2825A和LT8392/DC2626A4。

如下图所示

DC2825A采用直线MOSFET布置,DC2626A采用90°形状的MOSFET布置。为了进行公平比较,两个演示板配置了相同的MOSFET和解耦电容,并在36V转12V/10A、300kHz降压操作下进行了测试。图c显示了M1导通时刻测得的VIN交流纹波。

采用90°形状的MOSFET布置时,VIN纹波的幅度更低,谐振频率更高,这就验证了热回路路径较短导致PCB ESL更小。

相反,直线MOSFET布置的热回路更长,ESL更高,导致VIN纹波幅度要高得多,并且谐振频率更低。根据Cho和Szokusha研究的EMI测试结果,较高的输入电压纹波还会导致EMI辐射更严重4。

(a) LT8390/DC2825A热回路,MOSFET以直线布置;

(b) LT8392/DC2626A热回路,MOSFET以90°形状布置;

(c) M1导通时的VIN纹波波形。

深圳市福田区华强北路

深圳市福田区华强北路

1019号华强广场A座9J

0755-83212595

0755-83212595

139 2389 6490 微信

postmasterr@jingyeic.com

postmasterr@jingyeic.com

全球现货一站配齐

全球现货一站配齐 原厂代理分析授权

原厂代理分析授权 闪电发货配货快

闪电发货配货快